# Circuit Wizardry

**Grades:** Grades 4 and 5

**Team Size:** 1-3 competitors

**Duration:** 45 minutes

**Supervisors:** Tom Strait, Grant Kruger, Kendal Won

## Summary Description

Circuit Wizardry tests participants' knowledge of basic electrical circuit concepts, components, schematic reading and understanding, and ability to design and build a simple circuit from a functional description. The event is separated into three distinct parts. The three parts are:

- Part I: Understanding electrical circuit concepts and components

- Part II: Understanding electrical circuit functions and schematics

- Part III: Designing, building, testing and measuring electrical circuits

## Concepts Covered

- Electric charge and current (high level only)

- Units of measurement

- Conductors and insulators

- Types of electrical sources; difference between alternating current (AC) and direct current (DC)

- What is an electric circuit? Open vs. closed circuit, shorted circuits

- Schematic symbols, use and function of components (see Appendix)

- Voltage, current, resistance and units of measure

- Use of tools to measure with

- Ohm's law (and its impact on brightness of a lamp)

- Series and parallel circuits

- Schematic interpretation and design of circuit diagrams

- Building and troubleshooting simple DC circuits

- Resistance of networks of resistors

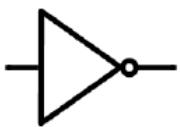

- Logic gates: Participants will be expected to name and specify the output of digital logic gates and networks (multi-level). These gates will include AND gates, OR gates, Inverter gates (NOT), and exclusive OR (XOR) gates.

## Rules/Competition Format

### **Part I**

Five multiple-choice questions about electrical circuit concepts and components will be asked. Concept questions may cover any of the topics listed in the Concepts Covered section of this document. Component questions may cover function, schematic symbol, use of resistor networks. Only components listed in the symbol reference and/or the materials section will be covered.

Participants will not be required to memorize component codes, such as resistor values.

### **Part II**

Two or three circuits or networks (for digital logic components or resistors (or circuits with networked resistors)) will be presented in schematic form to each team. The team will be asked to answer questions about the circuit or network function and operation. Those questions may require calculating a total resistance. Calculators will not be allowed, but individual resistor values will be chosen such that the math will fall within the state's grade specific standards.

### **Part III**

Teams will be given a functional description and a kit of components and asked to **design**, **build** and **measure** (5<sup>th</sup> grade teams only) a circuit that operates according to the functional description.

**Design** means drawing a schematic of a circuit. All components of the circuit must be labeled, in addition to using the correct circuit symbol. Failure to label a component will result in lost points.

**Build** means building an operational circuit using the available components.

**Measure** (5<sup>th</sup> grade teams only) means making and recording measurements of the circuit using a multimeter.

When a team has completed their exam, one team member will raise a hand and announce “done”. The team will review their design and demonstrate the circuit operation with the event supervisor. 5<sup>th</sup> grade teams will also report their circuit measurements.

## Clarifications and Notes

- 5<sup>th</sup> grade teams **must** bring their own multimeter. A digital multimeter is recommended, but not required. WESO has issued a digital multimeter to all schools this year.

- 4<sup>th</sup> grade teams **may** bring a multimeter to use for circuit troubleshooting. They will **not** be required to use it.

- Circuit measurements (5<sup>th</sup> grade teams only) will involve current, resistance and/or voltage

- A team **may** request assistance at any time if they believe that a component is defective. If it is determined by the event supervisor that the component is defective, it will be replaced and the team will be given a time credit, if needed. If the component is not defective, it will be returned to the team and no time credit will be given.

- A team **may** request assistance regarding interpretation of an exam question. The event supervisor will handle such questions on a case-by-case basis. No time credits will be given, however.

- A team **may not** request assistance regarding component function, use or operation.

- If one or more components used in the competition are in some way different from those provided in the kits, the event supervisor will indicate the differences to **all** teams before the start of the exam.

- Some components are not given explicitly, but may be simulated through a reduced function of a given component. For example, the kits contain a potentiometer and a DPDT switch – the components may be used to make a variable resistor (using two of the three potentiometer terminals) or an SPDT (using 3 of the 6 DPDT terminals). When designing their circuit in part 3 of the exam, the teams may either use the symbol of the actual component, or the component they are simulating (i.e. use of potentiometer with a fixed value as a resistor). In either case the proper use of the component must be drawn (i.e., the correct two terminals of the potentiometer must be used in the drawing if the team chooses to use the potentiometer symbol when it is being used as a variable resistor).

- Conventional current direction will be assumed throughout the event (positive to negative).

## Scoring

Points will be awarded for correct answers, descriptions, designs, labeling, units, operational circuits, and measurements. Score weighting for the different parts is as follows:

Part I: 10 points (2 points per question)

Part II: 20 points

Part III: 30 points (5th grade measurement will be part of 30 points)

**Total: 60** points

Final team ranking will be based on exam point totals.

## Tie Break Criteria

In the event of a tie, the following tie break criteria will be utilized (in order until the tie is broken)

1. Agreement between the drawn and built circuit in Section 3

2. The Circuit in Section 3 that is able to complete the function with the fewest number of nodes will win the tie-break

3. In the event there is still a tie, the score on a predesignated question from the exam will be used to try to break the tie

## Materials Distributed by WESO

- Source: Dual AA holder (1)

- Switches: SPST (2) and DPDT toggle (1)

- Resistors: 1, 10, 100, 1000  $\Omega$  (5 of each)

- Potentiometer: 100  $\Omega$  linear taper

- Diodes: 1 A (1)

- Light emitting diodes (LED) – 5mm, green and red (3 of each)

- Lamps: 1.5 V, 0.3 A (4)

- Lamp holders (2)

- Buzzers: 3V (1)

- Hook test leads (10)

- Multimeter (required for 5th grade, recommended for everyone)

- DC electric Motor

- Terminal Blocks on Board

- Jumper Wires

## Additional Materials and References useful for practices

- Other examples of circuitry (like Snap Circuit toys)

- Phet circuit simulations: <https://phet.colorado.edu/en/simulations/circuit-construction-kit-dc>

- Electronics Club: <https://electronicsclub.info/study.htm>

- Lists of Schematic symbols for logic elements and circuit components are on the WESO website (on this event's page).

## Materials to be brought to competition

- Multimeter only (required for 5th grade, optional for 4th grade)

## Example Questions

### Part I Example

What is the unit of measurement for electrical current?

### Part II Examples

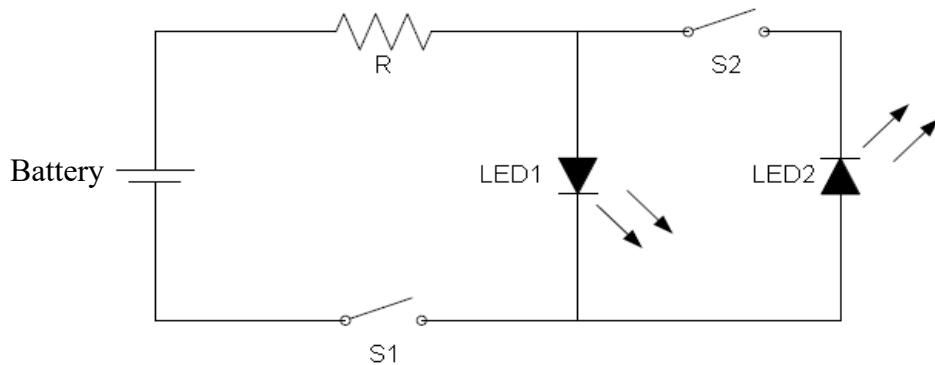

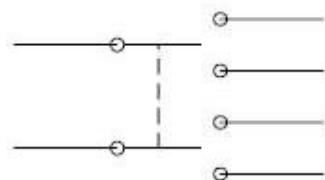

1. Given this circuit:

Assume the voltage and current are sufficient to turn on all LEDs. Describe what happens when both S1 and S2 are closed and when both S1 and S2 are open.

The switch scenarios may be also presented in the form of a State Table: each row will give the state of each switch (Open (off) or Closed (on)), the students will fill in the state of the lamp or LED (on or off).

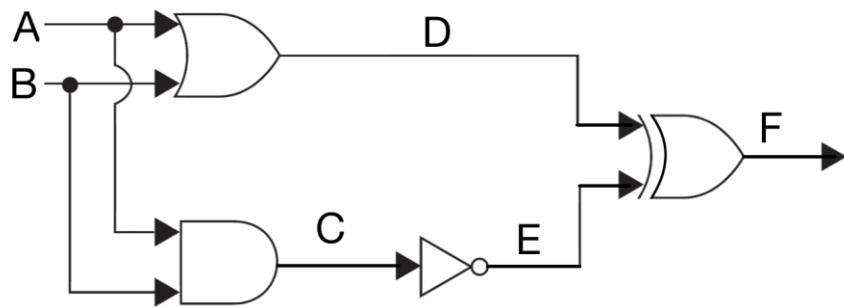

2. Find the combination(s) of input values A and B for which the output F equals 1.

Students should label all logic gates. Constructing a truth table may be helpful in solving this question.

### ***Part III Example***

Design and build a circuit that switches one lamp between off, low and high intensity. Switching may be done using any combination of switches.

Measure the current through the lamp when it is at high intensity (**5th grade only**).

## Appendix: Circuit Element Symbols

|       |                              |  |                            |

|-------|------------------------------|--|----------------------------|

|       | Wire with terminals          |  | Junction or connection     |

|       | Crossing, no connection      |  | Battery cell               |

|       | Resistor                     |  | Buzzer                     |

|       | Lamp                         |  | Lamp (alternate)           |

|       | Variable resistor            |  | Potentiometer              |

|       | Diode                        |  | LED (light emitting diode) |

| Anode | Diode terminals and polarity |  | DC Motor                   |

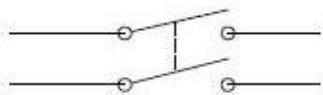

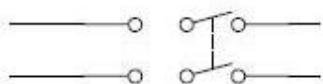

## Toggle Switches

Primary

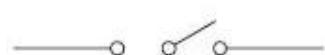

SPST (single pole, single throw)

Alternate

SPDT (single pole, double throw)

DPST (double pole, single throw)

DPDT (double pole, double throw)

## Logic Gate Symbols

| Logic Gate Symbol                                                                                 | Truth Table                                                                                                                                                                                                                                                                |        |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|---|---|---|---|---|---|---|---|---|---|---|---|

| <b>NOT</b><br>   | <table border="1"><thead><tr><th>Input</th><th>Output</th></tr></thead><tbody><tr><td>0</td><td>1</td></tr><tr><td>1</td><td>0</td></tr></tbody></table>                                                                                                                   | Input  | Output | 0      | 1 | 1 | 0 |   |   |   |   |   |   |   |   |   |

| Input                                                                                             | Output                                                                                                                                                                                                                                                                     |        |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| 0                                                                                                 | 1                                                                                                                                                                                                                                                                          |        |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| 1                                                                                                 | 0                                                                                                                                                                                                                                                                          |        |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| <b>AND</b><br>   | <table border="1"><thead><tr><th>Input1</th><th>Input2</th><th>Output</th></tr></thead><tbody><tr><td>0</td><td>0</td><td>0</td></tr><tr><td>0</td><td>1</td><td>0</td></tr><tr><td>1</td><td>0</td><td>0</td></tr><tr><td>1</td><td>1</td><td>1</td></tr></tbody></table> | Input1 | Input2 | Output | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 |

| Input1                                                                                            | Input2                                                                                                                                                                                                                                                                     | Output |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| 0                                                                                                 | 0                                                                                                                                                                                                                                                                          | 0      |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| 0                                                                                                 | 1                                                                                                                                                                                                                                                                          | 0      |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| 1                                                                                                 | 0                                                                                                                                                                                                                                                                          | 0      |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| 1                                                                                                 | 1                                                                                                                                                                                                                                                                          | 1      |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| <b>OR</b><br>  | <table border="1"><thead><tr><th>Input1</th><th>Input2</th><th>Output</th></tr></thead><tbody><tr><td>0</td><td>0</td><td>0</td></tr><tr><td>0</td><td>1</td><td>1</td></tr><tr><td>1</td><td>0</td><td>1</td></tr><tr><td>1</td><td>1</td><td>1</td></tr></tbody></table> | Input1 | Input2 | Output | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| Input1                                                                                            | Input2                                                                                                                                                                                                                                                                     | Output |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| 0                                                                                                 | 0                                                                                                                                                                                                                                                                          | 0      |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| 0                                                                                                 | 1                                                                                                                                                                                                                                                                          | 1      |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| 1                                                                                                 | 0                                                                                                                                                                                                                                                                          | 1      |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| 1                                                                                                 | 1                                                                                                                                                                                                                                                                          | 1      |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| <b>XOR</b><br> | <table border="1"><thead><tr><th>Input1</th><th>Input2</th><th>Output</th></tr></thead><tbody><tr><td>0</td><td>0</td><td>0</td></tr><tr><td>0</td><td>1</td><td>1</td></tr><tr><td>1</td><td>0</td><td>1</td></tr><tr><td>1</td><td>1</td><td>0</td></tr></tbody></table> | Input1 | Input2 | Output | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 |

| Input1                                                                                            | Input2                                                                                                                                                                                                                                                                     | Output |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| 0                                                                                                 | 0                                                                                                                                                                                                                                                                          | 0      |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| 0                                                                                                 | 1                                                                                                                                                                                                                                                                          | 1      |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| 1                                                                                                 | 0                                                                                                                                                                                                                                                                          | 1      |        |        |   |   |   |   |   |   |   |   |   |   |   |   |

| 1                                                                                                 | 1                                                                                                                                                                                                                                                                          | 0      |        |        |   |   |   |   |   |   |   |   |   |   |   |   |